# Characterization of Via Connections in Silicon Circuit Boards

JOHN P. QUINE, MEMBER, IEEE, HAROLD F. WEBSTER, SENIOR MEMBER, IEEE,

HOMER H. GLASCOCK, II, SENIOR MEMBER, IEEE,

AND RICHARD O. CARLSON

**Abstract**—Conducting vias isolated by silicon dioxide from a bulk silicon wafer and used to interconnect stripline transmission lines on opposite surfaces of the wafer are analyzed. The net VSWR and insertion loss for a single via and the crosstalk or coupling between two nearby vias are determined as a function of geometry, frequency, and silicon resistivity. For reasonable dimensions (geometries as mils and frequency to 1 GHz), the analysis predicts low VSWR and low insertion loss, provided the silicon resistivity is greater than about  $100 \Omega \cdot \text{cm}$ . It is shown that crosstalk can be small, and is mostly due to inductive coupling.

## I. INTRODUCTION

THE TREND TOWARD down-scaling of dimensions has led to shorter response times for VLSI chips. However, in order to realize this improved performance in an actual circuit, care must be taken to prevent signal degradation and delay in the interconnects between chips that are associated with conventional interconnection media such as printed circuit boards or ceramic multi-layers. Furthermore, the need for high signal propagation rates leads to the requirement that the conductors in the interconnection matrix, and the vias between them, be treated as high-speed transmission networks. These considerations have led to the proposal for a silicon circuit board as the interconnection medium, using much finer conductor lines and tighter spacings to achieve shorter interconnecting lengths.

Silicon circuit board configurations have been proposed previously [1]. However, the configuration discussed here is two-sided, with microstrip transmission lines and integrated circuit chips on both outer surfaces interconnected by vias. The fabrication of vias for the proposed configuration has been discussed previously [2], [3]. A principal objective of the present paper is to determine the minimum resistivity of the silicon that results in both low insertion loss for a single via and low coupling or crosstalk to other vias.

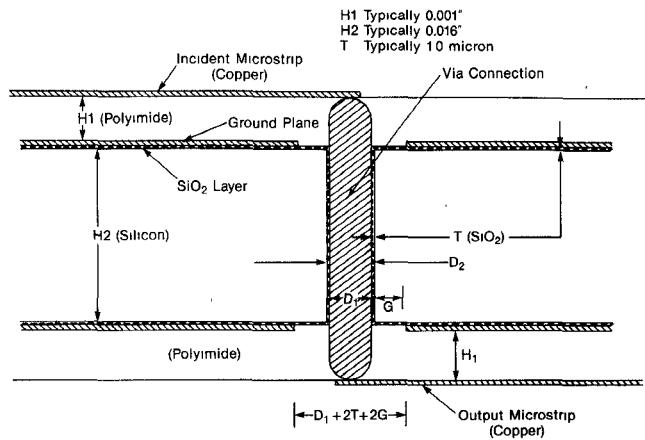

As shown in Fig. 1, the conducting ground planes are insulated from the silicon by a thin ( $1\text{-}\mu\text{m}$ ) layer of silicon dioxide ( $\text{SiO}_2$ ). Thin layers of polyimide on the ground

Fig. 1. Via connection between microstrip lines on silicon circuit board.

plane metallization form the dielectric for the microstrip transmission lines. The low dielectric constant (3.5) of the polyimide permits relatively high signal transmission rates. By employing thin polyimide layers, low crosstalk can be obtained even between closely spaced microstrip lines with relatively low signal attenuation and dispersion. The effect of the silicon resistivity on the reflection and transmission coefficients of a single via interconnection and on the coupling or crosstalk between two vias is determined. It is shown that the crosstalk is due mostly to inductive coupling.

## II. ANALYSIS

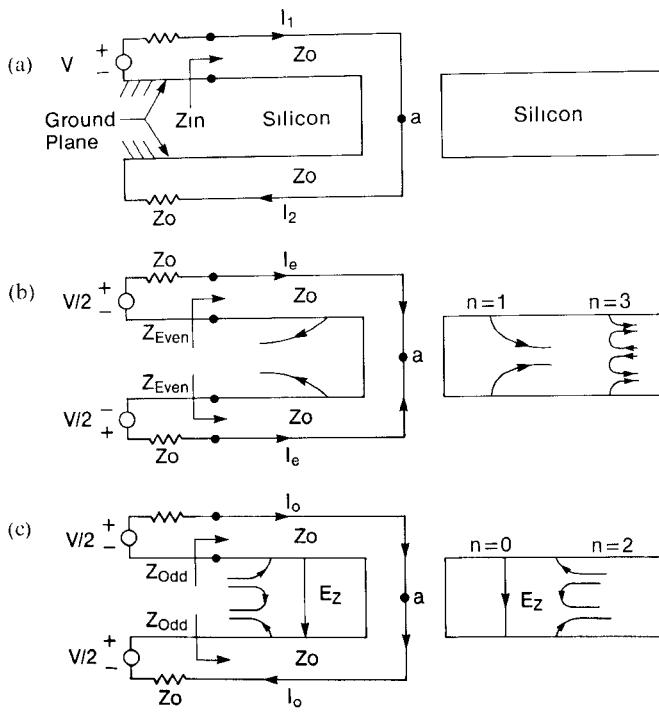

For small via diameters, the amplitudes of the higher order modes with angular dependence are small, and the relative orientation of the axes of the two interconnected microstrip lines has negligible effect. In this case, the electrical characteristics can be analyzed in terms of a single pair of even and odd modes of excitation, as shown in Fig. 2. Thus, the voltages and currents resulting when only a single microstrip line is excited can be represented as the summation of the voltages and currents corresponding to these two modes of excitation. By symmetry, the midpoint  $a$  of the via corresponds to an open-circuit point with even excitation, and a short-circuit point with odd excitation. Fig. 2 also shows the electric fields excited in the silicon region. The even excitation results in the evanescent  $\text{TM}_{0n}$  modes with  $n$  odd, while the odd excita-

Manuscript received February 16, 1987; revised August 5, 1987.

The authors are with the General Electric Company, Corporate Research and Development, Schenectady, NY 12301.

IEEE Log Number 8717900.

Fig. 2 Definition of the even and odd modes. (a) Single microstrip excited. (b) Even mode. (c) Odd mode.

tion results in the TEM ( $n = 0$ ) propagating mode along with  $TM_{0n}$  evanescent modes of negligible amplitudes with  $n$  even. Thus, the even excitation results mostly in capacitive energy storage in the silicon dielectric and dissipation due to the silicon conductivity, while the TEM mode associated with the odd excitation results in both inductive energy storage and radiation into the silicon region.

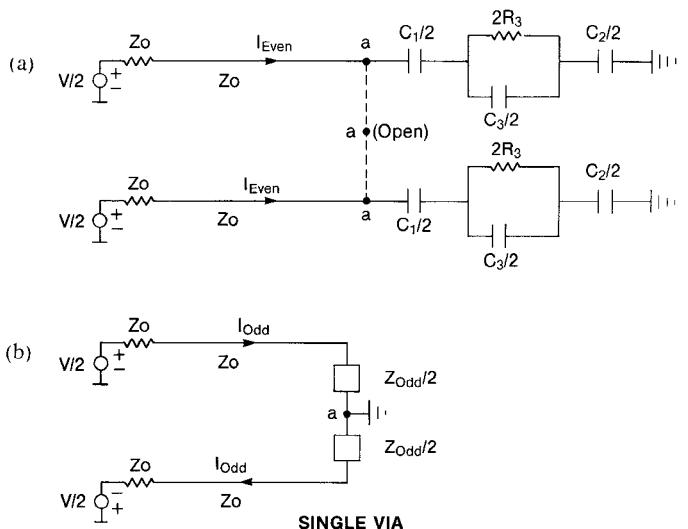

Fig. 3 shows approximate equivalent circuits.  $C_1$  is the capacitance between the via conductor and the silicon, and is approximately equal to the capacitance of a coaxial line of length  $H_2$  having inner and outer diameters equal to  $D_1$  and  $D_2$  and relative dielectric constant  $\epsilon_1$ , equal to that for  $SiO_2$  (3.78). Thus;

$$C_1 = 2\pi\epsilon_1\epsilon_0 H_2 / \ln(D_1/D_2) \quad (1)$$

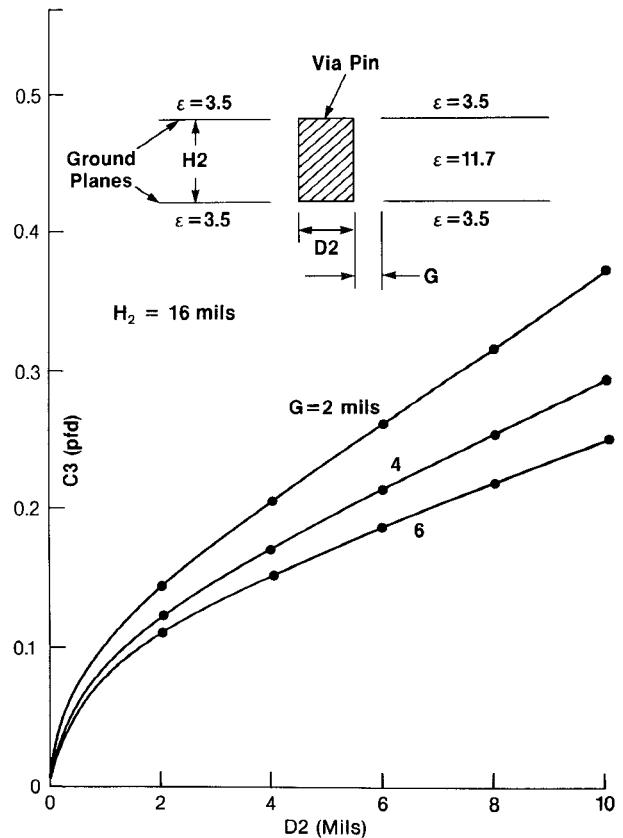

where  $\epsilon_0$  is the permittivity of free space. The determination of  $C_2$ , the capacitance between the silicon surface and the microstrip ground planes, is discussed in Appendix I.  $C_1$  and  $C_2$  act in series with net series value  $C_S$ . For the dimensions assumed,  $C_1 = 4.38$  pF,  $C_2 = 7.06$  pF, and  $C_S = 2.70$  pF. The elements  $C_3$  and  $R_3$  result from the fringing fields in the silicon region and are independent of frequency if the skin depth in the silicon region is much greater than  $H_2$ . The data in Fig. 4 calculated by the finite element method show that  $C_3$  is typically much less than  $C_S$ . Thus,  $C_3 = 0.25$  pF for  $G = 0.002$  in. It is assumed that  $R_3$  is given by  $\rho\epsilon'_2/C_3$ , where  $\rho$  is the resistivity and  $\epsilon'_2$  is the real part of the complex dielectric constant  $\epsilon_2$  of the silicon region. It can be seen that for very low silicon resistivity,  $R_3$  is small and the capacitance  $C_S$  is essentially connected directly to RF ground. Therefore, a high VSWR and insertion loss can result unless the silicon resistivity is significantly greater than the critical Maxwell-Wagner

Fig. 3 Equivalent circuits. (a) Even mode. (b) Odd mode.

Fig. 4 Calculated values of the fringing capacitance.

value [4], given approximately by

$$2\pi f_0 C_S R_3 = [2\pi f_0 \epsilon_2 C_S / C_3] \rho = 1.0 \quad (2)$$

where  $f_0$  is a designated center frequency equal to 0.5 GHz for the calculations in this paper. The value of  $\rho$  should be several times this critical value. For  $C_S = 2.7$  pF,  $C_3 = 0.25$  pF, and  $f_0 = 500$  MHz, the critical value of  $\rho$  is  $28 \Omega \cdot \text{cm}$ . For  $2\pi f_0 C_S R_3 \gg 1$ , the VSWR due to finite silicon resistivity approaches  $(1 + Z_0/R_3)$ .

For odd excitation, the dominant effect is due to the TEM mode, the capacitive effects due to the higher order

TM modes being small. If the radial waveguide extends to infinity (matched termination), then, as shown in Appendix II, the odd-mode impedance for small transverse dimensions is given by

$$Z_{\text{ODD}} = -j\sqrt{\frac{\mu}{\epsilon_{\text{EFF}}}} \left( \frac{H_2 + 2T}{2\pi a} \right) \frac{H_0(\lambda a)}{D_0(\lambda a)} \quad (3)$$

where  $a = D_2/2$ ,  $H_0(\lambda r)$  is the zero-order Hankel function of the second kind,  $D_0(\lambda a)$  is its derivative with respect to  $\lambda r$ ,  $\mu$  is the permeability, and

$$\epsilon_{\text{EFF}} = (H_2 + 2T)/(2T/\epsilon_1 + H_2/\epsilon_2) \quad (4)$$

= complex effective dielectric constant

$$\lambda = \sqrt{\omega^2 \mu \epsilon_{\text{EFF}}} \quad (5)$$

$$\epsilon_2 = \epsilon'_2 + 1/(j\omega\rho). \quad (6)$$

It should be noted that the form of (3) is the same as for a cylindrical wave in a homogeneous medium, but with  $\epsilon$  replaced by  $\epsilon_{\text{EFF}}$ . Furthermore, this value of  $\epsilon_{\text{EFF}}$  corresponds to the Maxwell-Wagner value for plane waves [4].

The following equation for  $Z_{\text{ODD}}$  is accurate when  $\omega\rho \gg 1$ .

$$Z_{\text{ODD}} \doteq R_{\text{ODD}} + jX_{\text{ODD}} \quad (7)$$

$$R_{\text{ODD}} = Z(\pi/2 - \phi) \quad (8)$$

$$X_{\text{ODD}} = Z \ln \left[ 2/\left( \gamma \beta a \sqrt{1 + \alpha^2/\beta^2} \right) \right] \quad (9)$$

$$\gamma = 1.78107$$

$$\alpha = (1/2\rho) \sqrt{\mu/\epsilon'_{\text{EFF}}}$$

$$\beta = \omega \sqrt{\mu \epsilon'_{\text{EFF}}}$$

$$Z = [(H_2 + 2T)/\lambda_0] (120\pi) (1 - \alpha^2/\beta^2)$$

$$\phi = \tan^{-1}(\alpha/\beta).$$

Here  $\lambda_0$  is the free-space wavelength, and  $\epsilon'_{\text{EFF}}$  is obtained by setting  $\epsilon_2 = \epsilon'_2$  in (4).

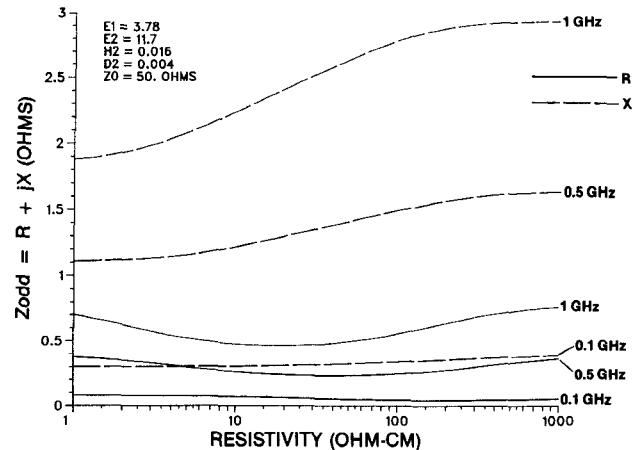

For typical dimensions, the real and imaginary parts of  $Z_{\text{ODD}}$  are both nearly independent of  $\rho$  and  $\epsilon'_2$ , and are small compared to the characteristic impedance  $Z_0$  of the microstrip line. Furthermore, the real part of  $Z_{\text{ODD}}$  is nearly independent of  $D_2$  for small  $D_2$ . Fig. 5 shows values of  $Z_{\text{ODD}}$  calculated from (3).

If the radial waveguide has a short-circuit termination at radius  $R_W$ , then  $Z_{\text{ODD}}$  is a pure reactance if  $\rho$  is infinite. However, in typical cases  $Z_{\text{ODD}}$  does not differ significantly from the value given by (3). The effect of the conducting walls is smaller, the smaller the resistivity of the silicon. Strong resonances, which result in  $Z_{\text{ODD}}$  being much greater than the value given by (3), occur only for high resistivity values. The lowest odd-mode resonant frequency is given by

$$F(\text{MHz}) \sqrt{\epsilon'_{\text{EFF}}} = 4522/R_W \text{ (inches) for } \bigcirc \text{ of radius } R_W \quad (10a)$$

$$F(\text{MHz}) \sqrt{\epsilon'_{\text{EFF}}} = 4173/R_W \text{ (inches) for } \square \text{ of side } 2R_W. \quad (10b)$$

Fig. 5. Calculated values of  $Z_{\text{ODD}}$ .

(a)

(b)

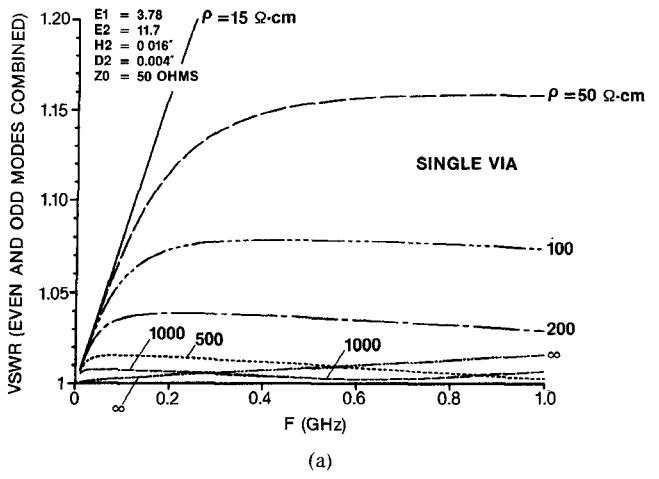

Fig. 6. (a) Calculated VSWR with even and odd modes combined. (b) Calculated insertion loss with even and odd modes combined.

The even-mode impedance is essentially unaffected by the conducting walls at  $r = R_W$ , unless the via is closer to the walls than about  $H_2/2$ .

The net VSWR and insertion loss was calculated by combining the even and odd modes. Calculations confirm that when the resistivity is less than the critical value, the even mode has a strong effect on VSWR, while the odd mode has only a small effect. Fig 6(a) shows that VSWR

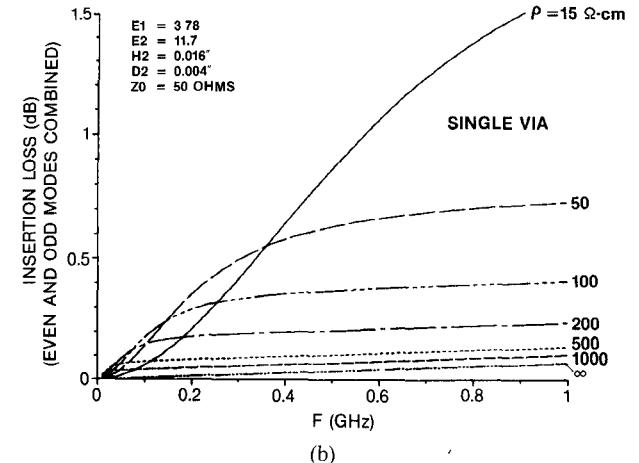

Fig. 7. (a) Calculated odd-mode isolation. (b) Equivalent circuit for even-mode coupling between two vias.

does not decrease steadily with increasing resistivity. Fig. 6(b) shows that minimum insertion loss occurs for infinite resistivity, but that the value of resistivity which results in maximum insertion loss depends on frequency. For the typical dimensions assumed, a value of resistivity greater than 100 to 200 Ω·cm results in low VSWR and insertion loss for frequencies up to 1.0 GHz.

The crosstalk or coupling between two vias is clearly small if the insertion loss for the single via is small. Noting that for VSWR less than 1.2 reflection loss is less than 0.036 dB, the data in Fig. 6 show that insertion loss for resistivity greater than 50 Ω·cm results mostly from power flow into the silicon region. Thus, with 200 Ω·cm the insertion loss is about 0.2 dB, and represents a loss of about 13 dB for the total power coupled into all of the radial waveguide modes. Additional reflection loss can be expected when radial waveguide power is incident on a second via. On this basis, the isolation between the two vias can be expected to be much greater than 13 dB, and perhaps as high as 26 dB. This has been confirmed by more detailed calculations of the crosstalk for both the even and odd modes of excitation. For example, the data in Fig. 7(a), calculated from the equations for  $E_Z$  in Appendix II, show that odd-mode isolation is typically 30

dB or more, and falls off relatively slowly with via separation because the coupled power is carried by the propagating TEM mode. Fig. 7(b) shows an equivalent circuit for calculating even-mode crosstalk between two vias. Coupling capacitance  $C_{12}$  was calculated by the finite-element method for the dimensions shown in Fig. 1, and for a via center-to-center separation of 0.016 in.  $R_{12}$  is given by  $\rho\epsilon_2'/C_{12}$ , and the even-mode complex coupling impedance  $Z_{12}$  is comprised of  $R_{12}$  and  $C_{12}$  in parallel. Even-mode isolation is given in Table I for these assumed dimensions. Because these dimensions result in  $|2Z_{12}| \gg R_3 \gg Z_0$ , even-mode isolation decreases with decreasing resistivity. Because the  $TM_1$  mode predominates for via separations greater than about  $H_2/2$ , even-mode isolation can be expected to increase by a factor of about 27.3 dB for an increase in via separation equal to one ground plane spacing  $H_2$ .

It is concluded that the even mode excites high impedance capacitive TM fields, which decay rapidly between the two ground planes. On the other hand, the odd mode excites mostly the propagating TEM mode, which has a low inductive impedance in the near field, and therefore is not strongly affected by  $\epsilon_2'$  or  $\rho$ . Thus, even for relatively small via separations, isolation for the even mode is much greater than for the odd mode, and net isolation is approximately that of the odd mode. The following equation gives the odd-mode isolation between two vias.

$$\text{Isolation} = 20 \log_{10} \left[ \left( \frac{2Z_{\text{ODD}}Z_0}{2Z_0 + Z_{\text{ODD}}} \right)^2 \cdot \left[ H_0(\lambda S)/H_0(\lambda a) \right] \right] \quad (11)$$

The following equation is accurate when  $Z_0 \gg Z_{\text{ODD}}$ ,  $\beta S \ll 1$ .

$$\text{Isolation (dB)} = -20 \log_{10} [K0\sqrt{K1^2 + K2^2}] \quad (12)$$

$$K0 = \omega\mu H_2/8Z_0$$

$$K1 = 1 - (\beta^2 - \alpha^2)S^1/4 - 2\phi/\pi$$

$$K2 = -(2/\pi) \left( \ln \left[ (S/2)\sqrt{\beta^2 + \alpha^2} \right] - M1 + 0.5772157 \right)$$

$$S = \text{center-to-center spacing of vias}$$

$$M1 = (\alpha\beta S^2)(\pi/4).$$

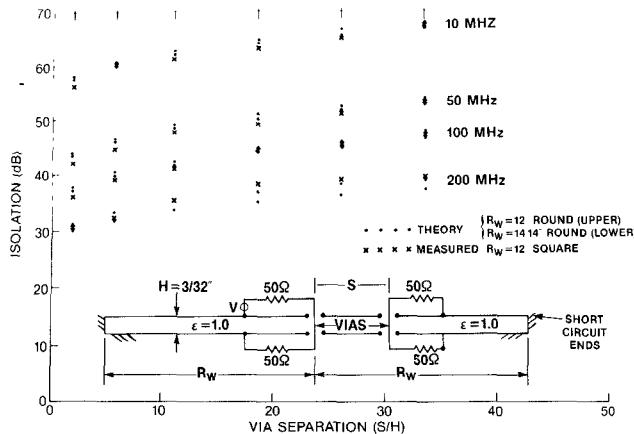

Equations (11) and (12) are also based on the assumption that the radial waveguide extends to infinity (matched termination). For short-circuit walls at  $r = R_W$ , high crosstalk between two vias can be expected for high resistivities at the resonant frequency given by (10). Fortunately, it is expected that most practical VLSI packages will not be complete metal enclosures, in which case cavity resonances should not present a serious problem. Good agreement was obtained between measured and calculated isolation, as shown in Fig. 8 for a simple air-filled, 24-in-square parallel-plate configuration having short-circuit terminations around the perimeter. For these calculations, (11) was modified to account for the short-circuit terminations.

TABLE I

EVEN-MODE ISOLATION (dB) FOR A VIA SEPARATION OF 0.016 IN

| $F$ (MHz) | $\rho = 15 \Omega \cdot \text{cm}$ | $\rho = 50 \Omega \cdot \text{cm}$ | $\rho = 200 \Omega \cdot \text{cm}$ | $\rho = 500 \Omega \cdot \text{cm}$ | $\rho = \infty$ |

|-----------|------------------------------------|------------------------------------|-------------------------------------|-------------------------------------|-----------------|

| 10        | 60.9                               | 68.9                               | 79.4                                | 83.0                                | 102.4           |

| 50        | 58.2                               | 66.7                               | 70.1                                | 73.9                                | 88.4            |

| 100       | 57.5                               | 63.2                               | 66.7                                | 72.7                                | 82.4            |

| 500       | 51.2                               | 55.0                               | 63.6                                | 67.2                                | 68.4            |

| 1000      | 48.3                               | 53.9                               | 60.8                                | 62.1                                | 62.4            |

Fig. 8. Measured and calculated isolation between two vias in air-filled parallel-plate configuration.

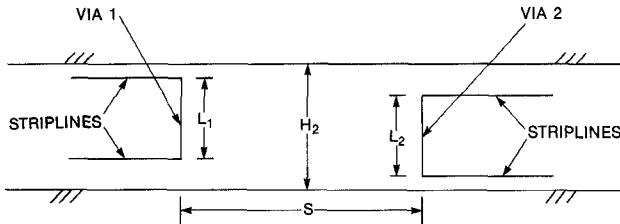

Fig. 9. Vias connecting strip lines between ground planes.

Note that a 26-in-diameter circle has about the same resonant frequency (eq. (10)) as a 24-in square.

The isolation between two vias connecting strip lines located between two ground planes as shown in Fig. 9 can be calculated by adding  $-20 \log_{10}(L_1 L_2 / H_2^2)$  to the value obtained from (11) or (12).

#### APPENDIX I CALCULATION OF $C_2$

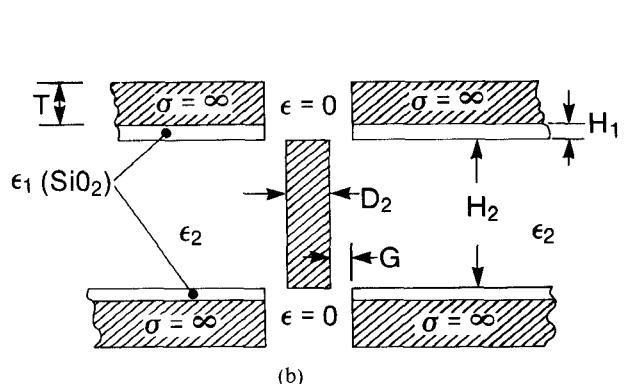

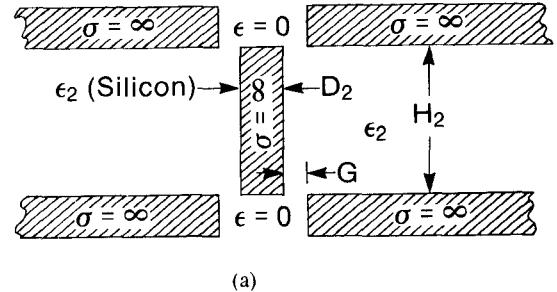

The capacitance  $C_2$  between the silicon surface and the microstrip ground planes is related approximately to the difference in capacitance of the via pin for the two configurations shown in Fig. 10. Note that the capacitance decreases when  $\text{SiO}_2$  layer is inserted. It is assumed that  $T \ll H_2$ , in which case the interface between the silicon and  $\text{SiO}_2$  is nearly an equipotential. The region with  $\epsilon = 0$  ensures that only flux passing through this interface is included. The value of  $C_2$  was calculated for the case  $H_2 = 0.016$  in,  $G = 0.002$  in,  $T = 1.0 \mu\text{m}$ ,  $\epsilon_1 = 3.78$ , and  $\epsilon_2 = 11.7$ . The calculated capacitances  $C_{3a}$  without and  $C_{3b}$  with the  $\text{SiO}_2$  layers were 0.20099 and 0.19548 pF, respectively.

Fig. 10. On the calculation of  $C_2$ . (a) With  $\text{SiO}_2$  layers removed. (b) With  $\text{SiO}_2$  layers inserted.

tively.  $C_2$  is determined by noting that this is the value of capacitance which, when placed in series with  $C_{3a}$ , results in the decreased capacitance  $C_{3b}$ . Thus,

$$C_2 = C_{3a} [C_{3a}/(C_{3a} - C_{3b}) - 1]. \quad (\text{A1})$$

On this basis,  $C_2$  is equal to 7.1 pF, compared to the calculated value of 4.38 pF for  $C_1$ . The series combination of  $C_1$  and  $C_2$  is  $C_S$ , equal to 2.7 pF.

#### APPENDIX II ODD-MODE IMPEDANCE

The fields for cylindrical waves in the outward radial direction are given below for the two-dielectric medium. Because the symmetry of the odd mode results in an effective conducting plane along the center of the Si layer, only a single  $\text{SiO}_2$  layer (region 1) and half the Si layer (region 2) are analyzed. The total odd-mode impedance is then twice the value calculated. The axis of the  $z$  coordinate coincides with the axis of the via conductor, and the plane  $z = 0$  lies along the interface between the Si and  $\text{SiO}_2$ . The odd-mode impedance is calculated at  $r = a = D_2/2$ .

In the  $\text{SiO}_2$  layer ( $z = 0$  to  $z = z_1 = T$ ),

$$E_{r1} = -E_{r0}(DOP)S_1(z)/S_1(0) \quad (A2)$$

$$E_{z1} = E_{r0}(\lambda/h_1)(HOP)C_1(z)/S_1(0) \quad (A3)$$

$$H_{\theta1} = -E_{r0}(j\omega\epsilon_1/h_1(DOP)C_1(z)/S_1(0) \quad (A4)$$

where

$$HOP = H_0(\lambda r)/D_0(\lambda a)$$

$$DOP = D_0(\lambda r)/D_0(\lambda a)$$

$$S_1(z) = \sin(h_1(z - z_1))$$

$$S_1(0) = \sin(h_1 z_1)$$

$$C_1(z) = \cos[h_1(z - z_1)]$$

$$C_1(0) = \cos(h_1 z_1).$$

$H_0(x)$  is the Hankel function of the second kind and  $D_0(x)$  is its derivative with respect to  $x$ .  $E_{r0}$  is the radial field at the boundary  $z = 0$  and  $r = a$ , and can be expressed in terms of the current flowing on the via. For any particular mode, the radial propagation constant  $\lambda$  must be the same in regions 1 and 2.

Similarly, in the silicon region ( $z = 0$  and  $z = -z_2 = -H_2/2$ ),

$$E_{r2} = -E_{r0}(DOP)S_2(z)/S_2(0) \quad (A5)$$

$$E_{z2} = E_{r0}(\lambda/h_2)(HOP)C_2(z)/S_2(0) \quad (A6)$$

$$H_{\theta2} = E_{r0}(j\omega\epsilon_2/h_2)(DOP)C_2(z)/S_2(0) \quad (A7)$$

where

$$S_2(z) = \sin(h_2(z + z_2))$$

$$S_2(0) = \sin(h_2 z_2)$$

$$C_2(z) = \cos(h_2(z + z_2))$$

$$C_2(0) = \cos(h_2 z_2).$$

Since  $E_{r1} = E_{r2}$  and  $H_{\theta1} = H_{\theta2}$  at  $z = 0$ , there results

$$\frac{h_1}{\epsilon_1} \tan(h_1 z_1) = -\frac{h_2}{\epsilon_2} \tan(h_2 z_2). \quad (A8)$$

Furthermore, from the wave equation

$$\lambda^2 = h_2^2 - k_2^2 = h_1^2 - k_1^2 \quad (A9)$$

where  $k_1^2 = \omega^2\mu\epsilon_1$  and  $k_2^2 = \omega^2\mu\epsilon_2$ . Equations (A8) and (A9) can be solved for  $h_1$  and  $h_2$  in terms of  $\epsilon_1$  and  $\epsilon_2$ , which in general are complex. The solution is simple if  $h_1 z_1$  and  $h_2 z_2$  are very small compared to unity, and applies accurately in the case of practical silicon circuit boards in which  $z_1 (= T)$  is small compared to the wavelength in region 1, and  $z_2 (= H_2/2)$  is small compared to the skin depth in the silicon. In this case, the fields in both regions can be nearly uniform, and the mode nearly TEM. The effects of conducting wall boundaries at a radius  $R_W$  were accounted for by considering both inward and outward radial waves. Resonances can be expected for finite  $R_W$  on the order of one-eight wavelength or more. Equation (3) for  $Z_{\text{ODD}}$ , which applies for  $R_W = \infty$ , can be

derived by defining a modal voltage  $V$  as  $(2TE_{z1}(a) + H_2 E_{z2}(a))$  and modal current  $I$  as  $-2\pi a H_0(a)$ . Hasegawa [5] and Krowne [6] have studied two-dielectric parallel-plate media. Limiting conditions were defined [5] for slow-wave, skin-effect, transition, and quasi-TEM "modes." The condition  $h_1 z_1, h_2 z_2 \ll 1$  excludes only the skin effect mode. This mode does not occur if the resistivity  $\rho$  is greater than

$$\rho \text{ MIN} = \omega\mu H_2^2/8.$$

For  $F = 1.0$  GHz and  $H_2 = 0.016$  in,  $\rho \text{ MIN} = 0.0163 \Omega \cdot \text{cm}$ . Thus, for all values of  $\rho > \rho \text{ MIN}$ , (3) and (4) are accurate for all frequencies  $< 1$  GHz.

## REFERENCES

- [1] R. W. Johnson *et al.*, "Hybrid silicon wafer-scale packaging technology," in *Proc. 1986 IEEE Int. Solid State Circuits Conf.*, Feb. 20, 1986, pp. 166-167.

- [2] J. F. McDonald, A. J. Steckl, C. A. Neugebauer, R. O. Carlson, and A. S. Bergendahl, "Multilevel interconnections for wafer scale integration," *J. Vac. Sci. Technol.*, vol. A4, no. 6, pp. 3127-3138, Nov./Dec. 1986.

- [3] H. H. Glascock, J. A. Loughran, and H. F. Webster, "Isolated conducting vias in silicon circuit boards," General Electric Co. Rep. 86CRD010 (class 1), Feb. 1986.

- [4] A. R. von Hippel, *Dielectrics and Waves*. New York: Wiley, 1954, pp. 228-234.

- [5] H. Hasegawa, M. Furukawa, and H. Yanai, "Properties of microstrip line in Si-SiO<sub>2</sub> systems," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-19, pp. 869-881, Nov. 1971.

- [6] C. M. Krowne, "Slow-wave propagation in two types of cylindrical waveguides loaded with a semiconductor," *IEEE Trans., Microwave Theory Tech.*, vol. MTT-33, pp. 335-339, Apr. 1985.

John P. Quine (S'48-M'85) was born in New York, NY, on January 11, 1923. He received the B.E.E., M.E.E., and Ph.D. degrees from Rensselaer Polytechnic Institute in 1949, 1952, and 1965 respectively.

During 1950 he was employed by the Cornell Aeronautical Laboratory, Buffalo, NY, as an electronics engineer. From 1950 to 1955 he was a member of the teaching and research staff of the Electrical Engineering Department at the Rensselaer Polytechnic Institute. In 1955 he joined the General Engineering Laboratory of the General Electric Company in Schenectady, NY, as a microwave engineer engaged in the development of microwave components and solid-state circuits. He has also conducted studies of phased array antennas. Dr. Quine is currently with the General Electric Research and Development Center in Schenectady, where he has continued to be involved in the general area of electromagnetic analysis. His recent work has included the analysis of microwave ovens, low-frequency coil configurations for NMR systems, power combiner/dividers, and the characterization of microwave integrated circuits and VLSI interconnections.

Dr. Quine is also an Adjunct Professor at Rensselaer Polytechnic Institute teaching an evening graduate course in microwave engineering. He is a member of Sigma Xi.

Harold F. Webster (SM'58) was born in Buffalo, NY, on June 25, 1919. He received the B.A. degree magna cum laude in 1941 and the M.A. degree in 1944 from the University of Buffalo. He received the Ph.D.

degree in 1953 from Cornell University, Ithaca, NY.

He was a Staff Member of the Massachusetts Institute of Technology Radiation Laboratory from 1943 to 1945, where he worked on waveguide components and microwave mixers. He joined the General Electric Research Laboratory in 1951, where he has worked on thermionic emission, photoelectric emission, adsorption phenomena, electron beam focusing, thermionic energy conversion, and power semiconductor packaging. He discovered the vortex instability in electron beams and was a cowinner of the IEEE 1958 W.R.G. Baker award. He was a delegate to the 13th General Assembly of the International Scientific Radio Union in London, 1960. He is the author of numerous papers and has been awarded 29 patents.

Dr. Webster is a member of the American Physical Society, Phi Beta Kappa, and Sigma Xi.

✖

**Homer H. Glascock, II (SM'79)** was born and raised near Hannibal, MO. He received the Ph.D. degree in physics from the University of Missouri at Columbia.

In 1960, he joined the General Electric Company Research & Development Center and is presently a member of the Power Semiconductor

Branch of CR&D. His work experience includes thermal properties of refractory oxides, thermionic cathodes, flame sensors, field emitters, X-ray image intensifiers, and electrodeless lamps. He has actively published journal articles and holds 15 patents. He is presently working on high-conductivity contacts for semiconductor devices.

Dr. Glascock is a member of the American Physical Society and Sigma Xi.

✖

**Richard O. Carlson** received the A.B., A.M., and Ph.D. degrees in physics from Columbia University, New York, NY, in 1947, 1949, and 1952, respectively.

Dr. Carlson joined the research staff of the General Electric Corporate Research and Development Center, Schenectady, NY, in 1954. His 1970's work involved power device and module packaging, solder fatigue problems, and sensors for temperature and humidity. Previously, he was manager of a Semiconductor Processing Facility, an in-house facility set up for silicon integrated circuit and device prototype processing. His earlier experimental studies were on GaAs laser diodes, thermoelectric materials, and deep-level impurities in silicon. His recent studies have been on VLSI packaging approaches, module layouts for bare chip-thin-film interconnects, and analysis of transient signals in transmission lines. He is the author of over 40 technical articles and has been awarded three U.S. Patents.